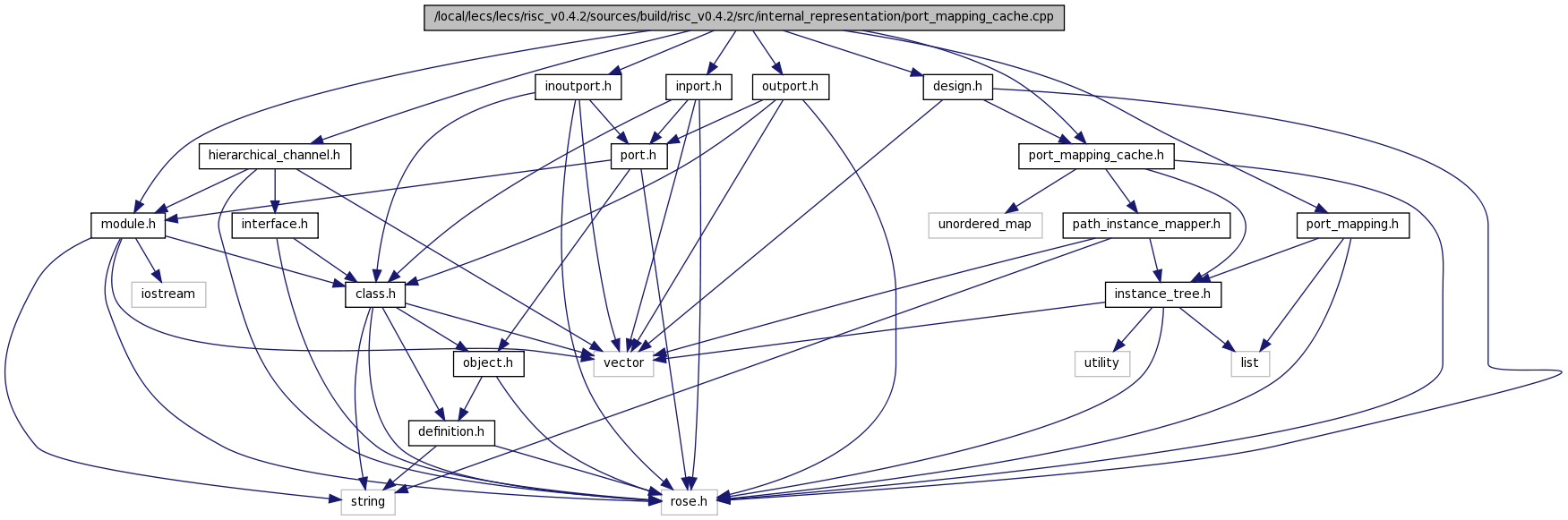

#include "port_mapping_cache.h"#include "design.h"#include "hierarchical_channel.h"#include "inoutport.h"#include "inport.h"#include "module.h"#include "outport.h"#include "port_mapping.h"

Defines | |

| #define | ANALYZE_PORT(PORT_TYPE, VAR_NAME) |

| #define | ANALYZE_PORT(PORT_TYPE, VAR_NAME) |

| #define ANALYZE_PORT | ( | PORT_TYPE, | |||

| VAR_NAME | ) |

for(risc:: PORT_TYPE \ iter_port = (*iter_hier_channel)-> VAR_NAME .begin(); \ iter_port != (*iter_hier_channel)-> VAR_NAME .end(); \ iter_port++) { \ SgVariableDefinition *port_var = (*iter_port)->get_ast_node(); \ std::list<risc::InstanceTree> ports \ = d->get_root().find_all_instances_of(port_var); \ for(std::list<risc::InstanceTree>::iterator \ port_path_iter = ports.begin(); \ port_path_iter != ports.end(); \ port_path_iter++) { \ int port_id \ = path_instance_mapper->get_id(*port_path_iter); \ InstanceTree channel_path \ = risc::get_mapped_channel_instance(*port_path_iter); \ int channel_id \ = path_instance_mapper->get_id(channel_path); \ mapping_[port_id][port_var] \ = std::pair<risc::InstanceTree, int>(channel_path, channel_id); \ } \ }

| #define ANALYZE_PORT | ( | PORT_TYPE, | |||

| VAR_NAME | ) |

for(risc:: PORT_TYPE \ iter_port = (*iter_module)-> VAR_NAME .begin(); \ iter_port != (*iter_module)-> VAR_NAME .end(); \ iter_port++) { \ SgVariableDefinition *port_var = (*iter_port)->get_ast_node(); \ std::list<risc::InstanceTree> ports \ = d->get_root().find_all_instances_of(port_var); \ for(std::list<risc::InstanceTree>::iterator \ port_path_iter = ports.begin(); \ port_path_iter != ports.end(); \ port_path_iter++) { \ int port_id \ = path_instance_mapper->get_id(*port_path_iter); \ InstanceTree channel_path \ = risc::get_mapped_channel_instance(*port_path_iter); \ int channel_id \ = path_instance_mapper->get_id(channel_path); \ mapping_[port_id][port_var] \ = std::pair<risc::InstanceTree, int>(channel_path, channel_id); \ } \ }

1.6.1

1.6.1