# Noise Margins of Threshold Logic Gates containing Resonant Tunneling Diodes

M. Bhattacharya and P. Mazumder

Department of Electrical Engineering and Computer Science

The University of Michigan

2215 EECS, 1301 Beal Avenue

Ann Arbor, MI 48109-2122 USA

### Abstract

Threshold gates consisting of RTDs in conjunction with HBTs or CHFETs or MOS transistors can form extremely compact, ultrafast, digital logic alternatives. The resonant tunneling phenomenon causes these circuits to exhibit super-high-speed switching capabilities. Additionally, by virtue of being threshold logic gates, they are guaranteed to be more compact than traditional digital logic circuits while achieving the same functionality. However, reliable logic design with these gates will need a thorough understanding of their noise performance and power dissipation among other things. In this paper, we present an analytical study of the noise performance of these threshold gates supplemented by computer simulation results, with the objective of obtaining reliable circuit design guidelines.

### 1 Introduction

Nanoelectronic devices based on the resonant tunneling phenomenon are poised to make a major impact on integrated circuit technology [1]. Over the years, a wide variety of circuits consisting of Resonant Tunneling devices have been proposed in the literature [2, 3, 4, 5, 6, 7, 8] which have given us the reason to believe that compact ultra-high-speed integrated circuits based on these types of devices will be physically realized in the near future. More recently, several researchers have reported the development of multi-gigahertz digital circuits [9, 10]. From their projected performance, logic circuits composed of Resonant Tunneling Diodes in conjunction with HBTs or MODFETs compare favorably with gates belonging to various other logic families (Table 1).

Circuits containing resonant tunneling devices, such as threshold gates, literals [11], multiplexers [3], counters and MOBILE gates [12, 13], are not only faster than the conventional circuits, but they also use far less number of devices to achieve the same functionality (Table 2).

Compared to the large number of published research papers dealing with the demonstration of RTD-based circuit operation and circuit ideas, work related to the analysis of such circuits seems to be very limited. This paper is a part of our continuing effort to fill that void.

## 2 RTD-HBT threshold logic gate

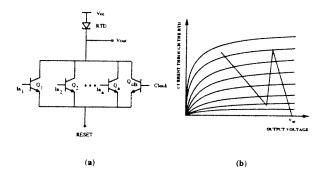

In this paper, we present a study of the noise immunity of a certain kind of RTD threshold gate whose circuit topology is shown in Fig. 1. This kind of circuit,

Table 2: Device counts for function implementation in various technologies

| Circuit          | TTL | CMOS | ECL | NDR |

|------------------|-----|------|-----|-----|

| XOR              | 33  | 16   | 11  | 4   |

| Majority         | 36  | 18   | 29  | 4   |

| Muller C-element | 45  | 8    | 44  | 4   |

| 9-state memory   | 24  | 24   | 24  | 5   |

| NOR2+flipflop    | 14  | 12   | 33  | 3   |

| NAND2+flipflop   | 14  | 12   | 33  | 3   |

Figure 1: The Circuit Topology (a) & Load line (b)

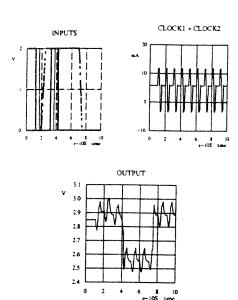

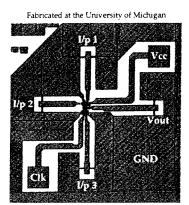

proposed by Mohan et al. [6], can be tailored to function as an n-input m-threshold gate (m-threshold => output is low, if and only if m or more inputs are high). The number n is related to the number of transistors (n+1) and m is determined by the input signal levels. For example, for n = 3 and m = 2, we can have a 3-input inverted-MAJORITY (or, MINORITY) gate. Simulation results of such a gate working at 10 GHz clock speed is shown in Fig. 2. The layout diagram of this circuit is shown in Fig. 3. By virtue of the generic nature of this gate, it is our opinion that, this type of RTD-HBT circuit may find wide application in the near future [14]. If the current drawn by each of the transistors  $Q_1, \ldots, Q_n$  in their ON states be I (assuming no transistor mismatch) and the current drawn by  $Q_{clk}$  be  $I_H$  (when Clock is HIGH) and  $I_Q$  (when Clock is QUIESCENT), then for an m-threshold gate function, the following basic necessary conditions have to be satisfied:

$$(m-1)I + I_{clkH} < I_p \tag{1}$$

Table 1: Comparison of process technologies

| Parameter                    | 0.5 μm CMOS                 | GaAs CHFET                  | RTD+HBT                 | RTD+MODFET              |

|------------------------------|-----------------------------|-----------------------------|-------------------------|-------------------------|

| Power/gate                   | 0.2 mW                      | 0.1 mW                      | 0.5 mW                  | 0.3 mW                  |

| Delay/gate                   | 500 ps                      | 250 ps                      | 40 ps                   | 200 ps                  |

| Device count<br>per function | Large due to<br>regular I-V | Large due to<br>regular I-V | Small due to<br>NDR I-V | Small due to<br>NDR I-V |

|                              | characteristics             | characteristics             | characteristics         | characteristics         |

Figure 2: Simulation results at 10 GHz clock speed of 3-input inverted-MAJORITY gate

$$I_{v} < mI + I_{clkL} < I_{p} \tag{2}$$

$$mI + I_{clkH} > I_p. (3)$$

### 3 Margin of noise on the signal lines

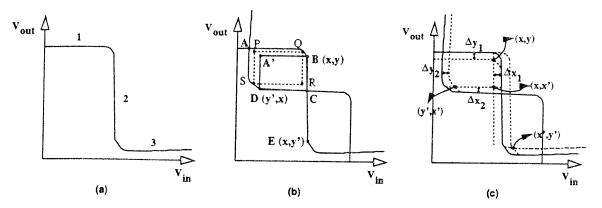

Noise margin measurement technique adopted in this work is based on the simple but accurate method of fitting a maximum area rectangle between the normal and mirrored transfer characteristics of an RTD-HBT inverter. This method has been shown to be by far the most general and precise method for characterizing noise margins [15].

If we consider the normal transfer characteristic of the RTD-HBT inverter (Fig. 4a), we see that Regions 1 and 3 are monotonically decreasing functions of  $V_{in}$  while Region 2 is an almost vertical drop. Region 2 is unique to the folded I-V characteristic of Resonant Tunneling devices which causes almost instantaneous switching of the output voltage, when the operating point skips over the unstable NDR region.

Important adjustments, however, are necessary in order to apply the above noise margin measurement philosophy to our circuit, simply because of the fact that this method is easy to apply to static digital gates, but is not applicable to clocked logic gates of the type we are currently concerned with. In RTD-HBT threshold gates, the clock voltage levels play an important role. While evaluating the inputs to a gate,

Figure 3: Layout diagram of 3-input inverted-MAJORITY gate

the level of the clock typically increases to  $V_H$  and after evaluation, this level decreases to a quiescent value of  $V_Q$ . If we consider two such RTD-HBT inverters connected in series, for proper operation, the clocks to the two inverters have to be out of phase. That is, when the second gate is being evaluated by a high clock pulse, the clock to the previous gate has to be quiescent. Simply stated, the transfer characteristic should reflect the fact that the second inverter sees the output of the first inverter with the clock at  $V_Q$  and not at  $V_H$ .

The folded I-V characteristic produces a sharp switching which can be regarded as a perfect vertical drop, for all practical purposes. Referring to Fig. 4b the maximum rectangle with the loop formed between the normal and the mirrored transfer characteristics will be A'BCD. If one tries to fit a rectangle of the type of PQRS, one can very soon realize that such a rectangle will almost always be smaller than A'BCD and in a special case, if PQRS > A'BCD,  $PQRS \approx A'BCD$ , since Regions 1 and 3 are almost horizontal. Thus A'BCD can be regarded as a good approximation of the maximum rectangle, in a general sense, within an area of the type ABCD. If the coordinates of the point B be (x, y) and that of point E be (x, y'), then the coordinates of the point D will be (y', x). Thus, the noise margins are simply expressed

$$NM_H = y - x, (4)$$

$$NM_L = x - y'. (5)$$

Therefore,

$$NM_H + NM_L = y - y'. (6)$$

Figure 4: The transfer characteristic at constant clock (a), finding the maximum area rectangle (b), & the effect of clock current fluctuation (c)

It is easily seen that

$$x = V_T \ln \left( \frac{I_p - I_H}{I_s \left( 1 - e^{-\frac{V_{cc} - V_p}{V_T}} \right)} \right), \quad (7)$$

where  $V_T = kT/q$ ,

$$y = (V_{cc} - V_p) + (I_H - I_Q)R_{p1},$$

(8)

$$y' = (V_{cc} - V_f) + (I_H - I_Q)R_{p2}.$$

(9)

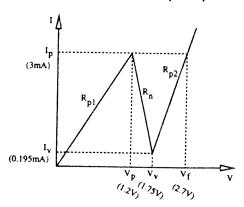

The symbols  $R_{p1}$ ,  $R_{p2}$ ,  $V_p$ ,  $V_f$ , etc., are explained with respect to the RTD's I-V characteristics in Fig. 5. Equation 7 is based on the simple exponential re-

Figure 5: The RTD used for computer simulations (not to scale)

lationship between a BJT's collector current and its base voltage

$$I_c = I_s \left( e^{\frac{V_{BE}}{V_T}} - e^{\frac{V_{BC}}{V_T}} \right). \tag{10}$$

This relationship is not very accurate and hence provides approximate results. For computer simulation, we shall use a more accurate relationship based on the

Gummel-Poon model of the bipolar transistor, but for the sake of deriving simple analytical Noise Margins, let us, for the moment, assume this relation. Equation 6 shows us that the sum of the two noise margins is independent of x and can be simply written as:

$$NM_H + NM_L = (V_f - V_p) + (I_H - I_Q)(R_{p1} - R_{p2}).$$

(11)

Since

$$R_{p2} = \frac{V_f - V_v}{I_p - I_v}, \tag{12}$$

$$|R_n| = \frac{V_v - V_p}{I_p - I_v},$$

(13)

$$NM_H + NM_L = (R_{p2} + |R_n|)(I_p - I_v) + (I_H - I_Q)(R_{p1} - R_{p2}).(14)$$

For proper operation of the gate,  $I_H < I_p$  and  $I_Q > I_v$ , implying,  $I_H - I_Q < I_p - I_v$ . Therefore, if  $R_{p1} \ge R_{p2}$ ,

$$NM_H + NM_L < (R_{p1} + |R_n|)(I_p - I_v)$$

or,  $NM_H + NM_L < V_v \left(1 - \frac{PVVR}{PVCR}\right)$ , (15)

where,

$PVVR = \text{Peak to Valley Voltage Ratio} = \frac{V_p}{V_v}$ and  $PVCR = \text{Peak to Valley Current Ratio} = \frac{I_p}{I_v}$ . On the other hand, if  $R_{p2} \ge R_{p1}$ ,

$$NM_H + NM_L < (R_{p2} + |R_n|)(I_p - I_v)$$

or,  $NM_H + NM_L < V_f - V_p$ . (16)

Inequations (15) and (16) give us important upper bounds for the sum of the two noise margins (when  $R_{p1} = R_{p2}$ , they are identical). On the one hand, they provide us with a simple way to estimate the maximum noise margin that can be harnessed from a given RTD, while on the other hand, they can be

used by the device engineers as a guideline for designing RTDs for digital logic applications. Diamond  $et\ al.$  [16] had shown that PVCR is not a crucial factor in determining RTD circuit switching speed. Their analysis had shown that  $C/I_P$  (where C is the RTD's capacitance) is a much more important figure that can be directly related to switching time. However, inequation 15 re-establishes, to a certain extent, the importance of PVCR so far as clocked RTD switching circuits are concerned. Furthermore, lower static power dissipation of such circuits is possible only when  $I_v$  is low. Thus, ultimately, PVCR remains an important figure of merit for the RTD beyond merely indicating the quality of epitaxial growth. For RTDs with PVCR in the range of 10-20 and above, inequation 15 reduces to

$$NM_H + NM_L \quad < \quad V_v. \tag{17}$$

Using Equation 10 we can write:

$$x = V_T ln \left( \frac{I_p - I_H}{I_s \left( 1 - e^{-\frac{V_{cc} - V_p}{V_T}} \right)} \right).$$

Therefore, the individual noise margins are given by:

$$NM_{H} = (V_{cc} - V_{p}) + (I_{H} - I_{Q})R_{p1}$$

$$-V_{T}ln\left(\frac{I_{p} - I_{H}}{I_{s}\left(1 - e^{-\frac{V_{cc} - V_{p}}{V_{T}}}\right)}\right), (18)$$

$$NM_{L} = V_{T}ln\left(\frac{I_{p} - I_{H}}{I_{s}\left(1 - e^{-\frac{V_{cc} - V_{p}}{V_{T}}}\right)}\right)$$

$$-(V_{cc} - V_{f}) - (I_{H} - I_{Q})R_{p2}. (19)$$

Therefore, in order to have  $NM_L = NM_H$ , we should have:

$$2V_T ln \left( \frac{I_p - I_H}{I_s \left( 1 - e^{-\frac{V_{cc} - V_p}{V_T}} \right)} \right) = 2V_{cc} - (V_p + V_f) + (I_H - I_Q)(R_{p1} + R_{p2}).$$

(20)

The accuracy of Equation 19 will be a subject of discussion in Section 5.

# 4 Noise margin with noise on the clock signal

So far, we have dealt with the noise margin estimates on the signal line without considering any noise on the clock inputs. Noise on the clocks will definitely lower the previously estimated signal noise margins. In order to study the worst case noise margins on the signal lines by introducing noise on the clock lines, we shall follow the following procedure.

We shall assume that noise on the clock lines can cause  $\pm \delta_I$  fluctuations in the quiescent and high clock currents. That is, instead of a steady value of  $I_Q$ , the quiescent clock can vary from  $I_Q - \delta_I$  to  $I_Q + \delta_I$ . Similarly, the high clock current can vary from  $I_H - \delta_I$  to  $I_H + \delta_I$ . We have to understand now how the three regions of the transfer characteristic will fluctuate with variations in the clock levels. Fig. 4c and Table 3 together provide the worst case situations that will adversely affect the noise margins. Based on them, the shrinkage of the noise margins can be approximately characterized by the Equations 21-24.

Table 3: Fluctuations in  $I_H \& I_Q$  and the resultant change in Noise Margins

| Fluctuation              | $I_H$    | $I_Q$      |  |

|--------------------------|----------|------------|--|

| $\Delta v_1$             | Increase | Increase   |  |

| $\frac{-31}{\Delta x_1}$ | Increase | Don't Care |  |

| $\Delta x_2$             | Decrease | Don't Care |  |

| $\frac{1}{\Delta y_2}$   | Decrease | Decrease   |  |

$$\Delta x_1 = V_T \ln \left( 1 + \frac{\delta_I}{I_p - I_H - \delta_I} \right), \qquad (21)$$

$$\Delta x_2 = V_T \ln \left( 1 + \frac{\delta_I}{I_p - I_H} \right), \qquad (22)$$

$$\Delta y_1 = \delta_I R_{p1}, \tag{23}$$

$$\Delta y_2 = \delta_I R_{p2}. \tag{24}$$

Therefore, the modified noise margins are:

$$NM_{H} = (V_{cc} - V_{p}) + (I_{H} - I_{Q} - \delta_{I})R_{p1} - V_{T} ln \left( \frac{I_{p} - I_{H} + \delta_{I}}{I_{s} \left( 1 - e^{-\frac{V_{cc} - V_{p}}{V_{T}}} \right)} \right), \quad (25)$$

$$NM_{L} = V_{T} ln \left( \frac{I_{p} - I_{H} - \delta_{I}}{I_{s} \left( 1 - e^{-\frac{V_{cc} - V_{p}}{V_{T}}} \right)} \right) - (V_{cc} - V_{f}) - (I_{H} - I_{Q} + \delta_{I})R_{p2}. \quad (26)$$

# 5 Computer simulation results

For the purpose of obtaining a general idea about the effect of various RTD and transistor parameters and the choice of current values  $(I_H\&I_Q)$ , the above equations should be sufficient. However, for accurate calculation of noise margins for a particular circuit, computer simulation seems to be the best approach. A computer simulation can handle the complex equations arising out of a detailed device model. For the RTD-HBT gate, we use the simple piecewise linear RTD model, but resort to the modified Gummel-Poon model of the bipolar transistor that is used in SPICE. Using an accurate model of the transistor is very essential, since the transistor plays a crucial role in determining the transfer function of these gates.

The collector current of a bipolar transistor, expressed in terms of the modified Gummel-Poon model parameters, is given by Equation 27.

$$I_{c} = \frac{I_{s}}{Q_{B}} \left[ \left( e^{\frac{V_{B^{\prime}E^{\prime}}}{N_{F}V_{T}}} - 1 \right) - \left( e^{\frac{V_{B^{\prime}C^{\prime}}}{N_{R}V_{T}}} - 1 \right) \right]$$

$$- \frac{I_{s}}{\beta_{R}} \left( e^{\frac{V_{B^{\prime}C^{\prime}}}{N_{R}V_{T}}} - 1 \right) - I_{SC} \left( e^{\frac{V_{B^{\prime}C^{\prime}}}{N_{C}V_{T}}} - 1 \right). \tag{27}$$

The noise margin calculations are carried out based on the methodology discussed in the previous section, by replacing the Equation 10 by Equation 27. The piecewise linear RTD characteristic used is shown in Fig. 5.

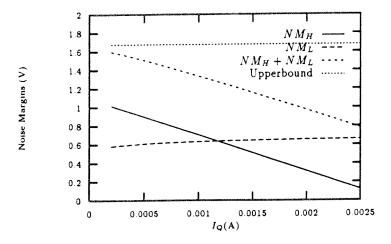

Fig. 6 shows the variation of an RTD-HBT inverter's noise margins as a function of the quiescent clock current  $I_Q$ . As we have seen before, the upperbound of the sum of the noise margins that can be extracted from an RTD is given by inequations 15 and 16. Practically, this upper-bound can never be reached because  $I_H$  has to be less than  $I_p$  and  $I_Q$  has to be greater than  $I_v$ , for proper operation. We see in Fig. 6, for a constant clock high current of 2.5 mA $(I_p = 3.08 \mathrm{mA})$  as  $I_Q$  is increased from  $I_v$  to  $I_H$ ,  $NM_H$  decreases fast while  $NM_L$  increases by a very small amount. While the behavior of  $NM_H$  is corroborated by Equation 18, the behavior of  $NM_L$  deviates considerably from Equation 19 at higher values of  $I_Q$ . This should not come as a surprise since the derivation of 19 assumes  $(V_{cc} - V_f)$  to be positive, while results presented in Fig. 6 were obtained using  $V_{cc} = 2V$ , making  $V_{cc} - V_f = -0.7V$ . Load lines drawn with  $V_{cc} < V_f$ will show us that the operating point after switching (from 1 to 0) has to be such that the transistor will be in saturation. From the above observation, it is clear that Equation 19 cannot be used when  $V_{cc} < V_f$ .

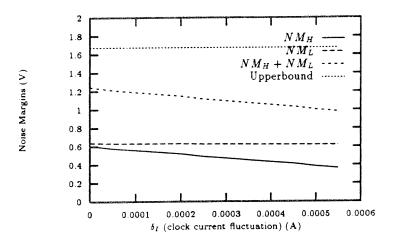

Next, we present computer simulation results by taking into account the noise on the clock signal as described in Section 4. For this purpose, we use Equation 27 to calculate the collector current of the transistor. In order to get accurate numerical results, we compute the coordinates (x,y) using  $I_H + \delta_I$  in place of  $I_H$  and  $I_Q + \delta_I$  in place of  $I_Q$  and (x',y') using  $I_H - \delta_I$  in place of  $I_Q$  and  $I_Q - \delta_I$  in place of  $I_Q$  [Fig. 4c] in accordance with Table 3. Thereafter, we calculate the noise margins as:

$$NM_H = y - x', (28)$$

$$NM_L = x - y'. \tag{29}$$

(It should be noted that Equations 25 and 26 are approximate forms of the above two equations).

Obviously, the noise on the clock line will have an effect of reducing the overall noise margin on the signal lines. Fig. 7 shows this effect. Interestingly,  $NM_L$  does not seem to be affected at all by the clock noise. This, in conjunction with the fact that  $NM_H$  decreases with increasing  $\delta_I$ , tells us that the choice of  $I_H$  and  $I_Q$  should not be such that  $NM_H = NM_L$ . In fact, a robust design that can tolerate a larger amount of noise in the clock line, should have  $I_H$  and  $I_Q$  that make  $NM_H > NM_L$ .

### 6 Conclusions

The noise margin evaluation procedure presented in this paper, can be extremely useful in the design of threshold gates using RTD. We have shown that an upper-bound on the sum of the noise margins  $(NM_H + NM_L)$  that can be extracted from a given RTD, irrespective of the type of transistors used, can be obtained by using inequations 15 and 16. Our analysis shows that the choice of the clock currents  $I_Q$  and  $I_H$  should be guided by Equations 18, 19 and Equations 25, 26, but the final choice should be made after computer simulations of the form presented in Section 5. This is because, when the output is LOW, the transistors are in saturation and Equation 27 is definitely superior to Equation 10 which tends to overestimate  $NM_L$ . The analysis presented in this paper is for RTD threshold gate circuits with bipolar transistors as pull down devices. Analysis of threshold gates for other types of transistors should be similarly performed. Since RTD circuits are meant to be used at ultra-high speeds, the sharp rising and falling edges of the clock and signal lines, coupled with the inductances associated with the interconnects will produce what is known as  $\Delta I$ -noise. The analysis presented above should be adequate in taking these ringing effects into account.

## Acknowledgment

The authors wish to thank Dr. Masafumi Yamamoto of NTT System Electronics Laboratories, Japan, and Shriram Kulkarni of the University of Michigan.

#### References

- J. Randall, G. Frazier, A. Seabaugh, and T. Broekaert, "Potential nanoelectronic integrated circuit technologies," *Micrelectronic Engineering*, vol. 32, pp. 15-30, September 1996.

- [2] F. Capasso, S. Sen, F. Beltram, L. M. Lunardi, A. S. Vengurlekar, P. R. Smith, N. J. Shah, R. J. Malik, and A. Y. Cho, "Quantum functional devices: resonant-tunneling transistors, circuits with reduced complexity and multiple-valued logic," *IEEE Transactions on Electron Devices*, vol. 36, pp. 2065-2082, October 1989.

- [3] H. L. Chan, S. Mohan, P. Mazumder, and G. I. Haddad, "Compact multiple-valued multiplexers using negative differential resistance devices," *IEEE Journal of Solid-State* Circuits, vol. 31, pp. 1151-1156, August 1996.

- [4] C. E. Chang, P. M. Asbeck, K. C. Wang, and E. R. Brown, "Analysis of heterojunction bipolar transistor/resonant tunneling diode logic for low-power and high-speed digital applications," *IEEE Transactions on Electron Devices*, vol. 40, pp. 685-691, April 1993.

- [5] K. Maezawa and T. Mizutani, "A New Resonant Tunneling Logic Gate Employing Monostable-Bistable Transition." Japanese Journal of Applied Physics, Part 2, Letters, vol. 32, pp. L42-L44, January 1993.

- [6] S. Mohan, P. Mazumder, R. K. Mains, J. P. Sun, and G. I. Haddad, "Logic design based on negative differential resistance characteristics of quantum electronic devices," *IEE Proceedings, Part G: Circuits, Devices and Systems*, vol. 140, pp. 383-391, December 1993.

- [7] K. J. Chen, T. Waho, K. Maezawa, and M. Yamamoto, "Exclusive-or logic circuit based on controlled quenching of series-connected negative differential resistance devices," *IEEE Electron Device Letters*, vol. 17, pp. 309-311, June 1996.

- [8] K. J. Chen, K. Maezawa, T. Waho, and M. Yamamoto, "Device technology for monolithic integration of InP-based

Figure 6: Noise margins vs. quiescent clock current  $(V_{cc}=2V)$

Figure 7: Noise margins vs.  $\delta_I$

resonant tunneling diodes and HEMTs." IEICE Transactions on Electronics, vol. E79-C, pp. 1515-1524. November 1996.

- [9] W. Williamson, S. B. Enquist, D. H. Chow, H. L. Dunlap, S. Subramaniam, P. Lei, G. H. Bernstein, and B. K. Gilbert, "12 GHz clocked operation of ultralow power interband resonant tunneling diode pipelined logic gates," *IEEE Journal of Solid-State Circuits*, vol. 32, pp. 222-231, February 1997.

- [10] K. Maezawa, H. Matsuzaki, K. Arai, T. Otsuji, and M. Yamamoto, "High-speed operation of resonant tunneling flip-flop circuit employing a MOBILE (monostable-bistable transition logic element)," in Digest of the 55th IEEE Annual Device Research Conference, (Fort Collins, Colorado), pp. 94-95, June 1997.

- [11] T. Waho, K. J. Chen, and M. Yamamoto, "Literal gate using resonant-tunneling devices," in Proceedings of the International Symposium on Multiple-Valued Logic, (Los Alamitos, CA), pp. 68-73, IEEE, 1996.

- [12] K. Maezawa, T. Akeyoshi, and T. Mizutani, "Functions and applications of monostable-bistable transition logic elements (MOBILE's) having multiple-input terminals,"

- IEEE Transactions on Electron Devices, vol. 41, pp. 148-154, February 1994.

- [13] K. Maezawa, "Analysis of switching time of monostable-bistable transition logic elements based on simple model calculation," Japanese Journal of Applied Physics, Part 1, vol. 34, pp. 1213-1217, February 1995.

- [14] P. Mazumder, S. Kulkarni, M. Bhattacharya, J. P. Sun, and G. I. Haddad, "Digital circuit applications of resonant tunneling devices," *IEEE Proceedings*, 1998. To appear.

- [15] J. R. Hauser, "Noise Margin Criteria for Digital Logic Circuits," IEEE Transactions on Education, vol. 36, pp. 363-368, November 1993.

- [16] S. Diamond, E. Ozbay, M. J. W. Rodwell, D. M. Bloom, Y. C. Pao, and J. S. Harris, "Resonant tunneling diodes for switching applications," Applied Physics Letters, vol. 54, pp. 153-155, January 1989.