# Embedded Systems Environment Back End

## ESE Technology

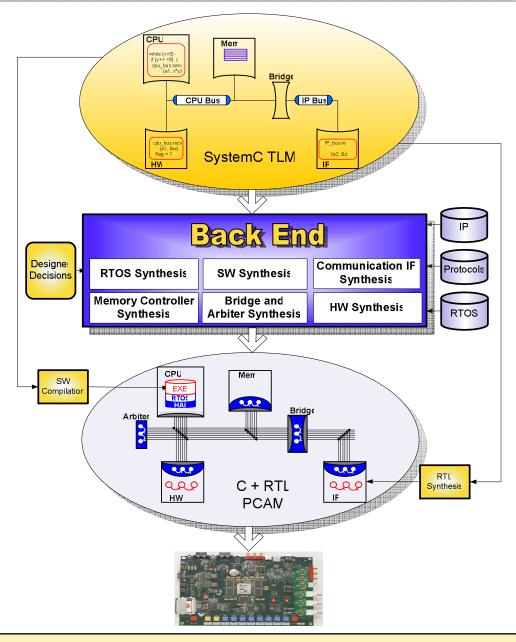

Today's embedded system designs are complex heterogeneous platforms consisting of multiple standard and custom processors, each with possibly different interface, communicating over a network of busses and bridges.

System design tools are needed for prototyping such platforms with FPGA or ASIC technologies. ESE **incorporates more than 15 years of research and development** in system languages, synthesis and verification to provide automatic system prototyping from TLM.

| C | Specification Model Capture |               |                       |

|---|-----------------------------|---------------|-----------------------|

|   | 7. Application              |               | 7. Application        |

|   | 6. Presentation             | Spec          | 6. Presentation       |

|   | 5. Session                  | TLM           | 5. Session            |

|   | 4. Transport                |               | 4. Transport          |

|   | 3. Network                  |               | 3. Network            |

|   | 2c. Link + Stream           |               | 2c. Link + Stream     |

|   | 2b. Media Access Ctrl       |               | 2b. Media Access Ctrl |

| - | 2a. Protocol                |               | 2a. Protocol          |

|   | 1. Physical                 |               | 1. Physical           |

|   |                             | Address Lines |                       |

**ESE Back End** helps system designers by automatically synthesizing system prototypes from the given Transaction Level Models (TLMs). System designers can create, modify and test their platforms in a few days compared to months of RTL coding and simulation. They can quickly make board prototypes available to application developers for generating and validating critical SW and HW interactions across multiple cores

### **ESE** Features

#### **Graphical Entry**

TLM capture with application C code and platform specification.

Automatic system SW generation for each processor.

Cycle accurate RTL synthesis for all interfaces and HW cores.

Automatic bridge generation for protocol translation between incompatible cores.

#### FPGA/ASIC-ready output

The output model has synthesizable RTL for all HW and drivers with application C code for downloading to embedded processors.

## **Embedded Systems Environment Back End**

## **Designer Advantages**

- No need to learn system level modeling style or languages  $\rightarrow$ No need to develop synthesizable RTL code for HW interfaces

- Automatic RTL generation → Automatic SW generation →

$\rightarrow$

TLM is easier to debug and fix

**Graphical entry to ESE**

No need to develop processor and platform specific system SW

No need to simulate, learn and debug cycle accurate models

## **Management Benefits**

→

$\rightarrow$

Automatic system design from TLM Synthesizable RTL/C output

- Design decisions and TLMs can be shared → →

- TLMs can be easily reused and extended

- 1000X productivity gain in modeling and verification

- Easy fit with existing tools, minimal training time

- Simplified globally-distributed collaboration

- Easier product upgrade and customization